# MOS INTEGRATED CIRCUIT $\mu$ PD16326

#### 32-BIT FLUORESCENT DISPLAY TUBE DRIVER

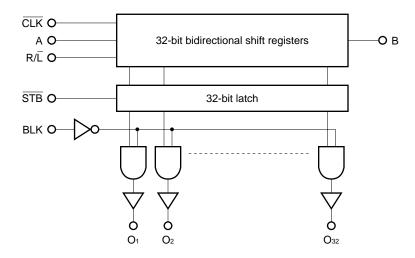

The  $\mu$ PD16326 is a fluorescent display tube driver using a high breakdown voltage CMOS process. It consists of 32-bit bidirectional shift registers, a latch circuit, and a high breakdown voltage CMOS driver block. The logic block operates on a 5 V power supply designed to be connected directly to a microcontroller (CMOS level input). The driver block has a 130 V and 20 mA high breakdown voltage output, and both the logic block and driver block consist of CMOS, allowing operation with low power consumption.

#### **FEATURES**

- High breakdown voltage CMOS structure

- High breakdown voltage, high current output (130 V, 20 mA)

- · 32-bit bidirectional shift registers on chip

- Data control by transfer clock (external) and latch

- High-speed data transfer capability (fmax = 8.0 MHz MIN)

- Wide operating temperature range (T<sub>A</sub> = -40 to 85 °C)

#### ORDERING INFORMATION

| Part Number    | Package                                |

|----------------|----------------------------------------|

| μPD16326GB-3B4 | 44-pin plastic QFP (4-direction leads) |

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

#### **BLOCK DIAGRAM**

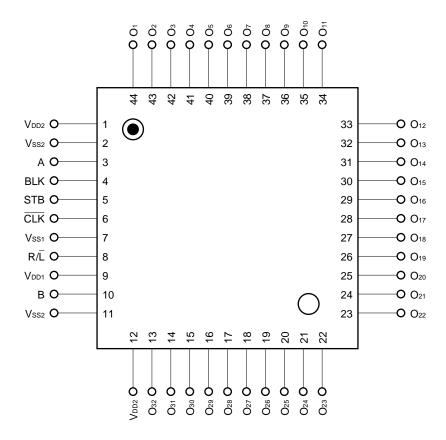

# PIN CONFIGURATION (Top View)

**Remark** Be sure to enter the power to V<sub>DD1</sub>, logic signal, and V<sub>DD2</sub>, in that order, and turn off the power in the reverse order.

#### PIN DESCRIPTION

| Pin Symbol                        | Pin Name                      | Pin Number | Description                                                                                                                                                                        |

|-----------------------------------|-------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STB                               | Latch strobe input            | 5          | H: Data through L: Data retention                                                                                                                                                  |

| А                                 | RIGHT data input              | 3          | When $R/L = H$ , A: Input B: Output                                                                                                                                                |

| В                                 | LEFT data input               | 10         | When R/L = L, A: Output B: Input                                                                                                                                                   |

| CLK                               | Clock input                   | 6          | Shift is executed on a fall.                                                                                                                                                       |

| BLK                               | Blanking input                | 4          | H: O <sub>1</sub> to O <sub>32</sub> : ALL "L"                                                                                                                                     |

| R/L                               | Shift control input           | 8          | $\begin{array}{lll} \text{H: Right shift mode} & A \rightarrow O_1 \ \ O_{32} \rightarrow B \\ \text{L: Left shift mode} & B \rightarrow O_{32} \ \ O_1 \rightarrow A \end{array}$ |

| O <sub>1</sub> to O <sub>32</sub> | High breakdown voltage output | 13 - 44    | 130 V, 20 mA MAX                                                                                                                                                                   |

| V <sub>DD1</sub>                  | Logic block power supply      | 9          | 5 V ±10 %                                                                                                                                                                          |

| V <sub>DD2</sub>                  | Driver block power supply     | 1, 12      | 30 to 125 V                                                                                                                                                                        |

| Vss1                              | Logic ground                  | 5          | Connected to system GND                                                                                                                                                            |

| Vss2                              | Driver ground                 | 2, 11      | Connected to system GND                                                                                                                                                            |

# TRUTH TABLE 1 (SHIFT REGISTER BLOCK)

| Input |          | Out          | tput         | Chift Dogistor           |

|-------|----------|--------------|--------------|--------------------------|

| R/L   | CLK      | А            | В            | Shift Register           |

| Н     | <b>\</b> | Input        | OutputNote 1 | Execution of right shift |

| Н     | H or L   |              | Output       | Retained                 |

| L     | <b>\</b> | OutputNote 2 | Input        | Execution of left shift  |

| L     | H or L   | Output       |              | Retained                 |

Notes 1. On a clock fall, the data items of  $S_{31}$  are shifted to  $S_{32}$ , and output from B.

2. On a clock fall, the data items of  $S_2$  are shifted to  $S_1$ , and output from A.

# TRUTH TABLE 2 (LATCH BLOCK)

| STB | Operation                                         |

|-----|---------------------------------------------------|

| L   | Retains S₁ data immediately before STB becomes L. |

| Н   | Outputs shift register data.                      |

# TRUTH TABLE 3 (DRIVER BLOCK)

| LnNote | STB | BLK | Driver output state          |

|--------|-----|-----|------------------------------|

| ×      | ×   | Н   | L (all driver outputs: L)    |

| ×      | L   | L   | Outputs S₁ data on STB fall. |

| L      | Н   | L   | L                            |

| Н      | Н   | L   | Н                            |

Note Ln: Latch output

**Remark**  $\times = H$  or L, H = high level, L = Low level

# ABSOLUTE MAXIMUM RATINGS (TA = 25 °C, Vss = 0 V)

| Item                                | Symbol           | Rating                         | Unit |

|-------------------------------------|------------------|--------------------------------|------|

| Logic block supply voltage          | V <sub>DD1</sub> | -0.5 to +7.0                   | V    |

| Driver block supply voltage         | V <sub>DD2</sub> | -0.5 to +130                   | V    |

| Logic block input voltage           | Vı               | -0.5 to V <sub>DD1</sub> + 0.5 | V    |

| Driver block output current         | lo               | 20                             | mA   |

| Package allowable power dissipation | Po               | 800Note                        | mW   |

| Operating ambient temperature       | TA               | -40 to +85                     | °C   |

| Storage temperature                 | T <sub>stg</sub> | -65 to +150                    | °C   |

Note When  $T_A \ge 25$  °C, load should be alleviated at a rate of -8.0 mW/°C. ( $T_j = 125$  °C  $_{(MAX.)}$ )

# RECOMMENDED OPERATING RANGE ( $T_A = -40 \text{ to } +85 \text{ °C}$ , $V_{SS} = 0 \text{ V}$ )

| Item                        | Symbol           | MIN.                 | TYP. | MAX.                 | Unit |

|-----------------------------|------------------|----------------------|------|----------------------|------|

| Logic block supply voltage  | V <sub>DD1</sub> | 4.5                  | 5.0  | 5.5                  | V    |

| Driver block supply voltage | V <sub>DD2</sub> | 30                   |      | 125                  | V    |

| Input voltage high          | ViH              | 0.7·V <sub>DD1</sub> |      | V <sub>DD1</sub>     | V    |

| Input voltage low           | VIL              | 0                    |      | 0.2·V <sub>DD1</sub> | V    |

| Driver output current       | Іон              |                      |      | -10                  | mA   |

|                             | loL              |                      |      | +2.5                 | mA   |

# ELECTRICAL SPECIFICATIONS (TA = 25 $^{\circ}$ C, VDD1 = 4.5 to 5.5 V, VDD2 = 125 V, Vss = 0 V)

| Item                       | Symbol            | Condition                                                     | MIN.                 | TYP. | MAX.                 | Unit |

|----------------------------|-------------------|---------------------------------------------------------------|----------------------|------|----------------------|------|

| Output voltage high        | V <sub>OH1</sub>  | Logic, Iон = -1.0 mA                                          | 0.9·V <sub>DD1</sub> |      | V <sub>DD1</sub>     | V    |

| Output voltage low         | V <sub>OL1</sub>  | Logic, IoL = 1.0 mA                                           | 0                    |      | 0.1·V <sub>DD1</sub> | V    |

| Output voltage high        | V <sub>OH21</sub> | O <sub>1</sub> to O <sub>40</sub> , I <sub>OH</sub> = -0.5 mA | 121                  |      |                      | V    |

|                            | V <sub>OH22</sub> | O <sub>1</sub> to O <sub>40</sub> , I <sub>OH</sub> = -5.0 mA | 115                  |      |                      | V    |

| Output voltage low         | V <sub>OL2</sub>  | O <sub>1</sub> to O <sub>40</sub> , I <sub>OL</sub> = 0.5 mA  |                      |      | 2.5                  | V    |

| Input leakage current      | lı∟               | VI = VDD1 Or VSS1                                             |                      |      | ±1.0                 | μΑ   |

| Input voltage high         | ViH               |                                                               | 0.7·V <sub>DD1</sub> |      | V <sub>DD1</sub>     | V    |

| Input voltage low          | VIL               |                                                               | 0                    |      | 0.2·V <sub>DD1</sub> | V    |

| Static consumption current | I <sub>DD1</sub>  | Logic, $T_A = -40$ to +85 °C                                  |                      |      | 1 000                | μΑ   |

|                            | I <sub>DD1</sub>  | Logic, T <sub>A</sub> = 25 °C                                 |                      |      | 100                  | μΑ   |

|                            | I <sub>DD2</sub>  | Driver, $T_A = -40$ to +85 °C                                 |                      |      | 1 000                | μΑ   |

|                            | I <sub>DD2</sub>  | Driver, T <sub>A</sub> = 25 °C                                |                      |      | 100                  | μΑ   |

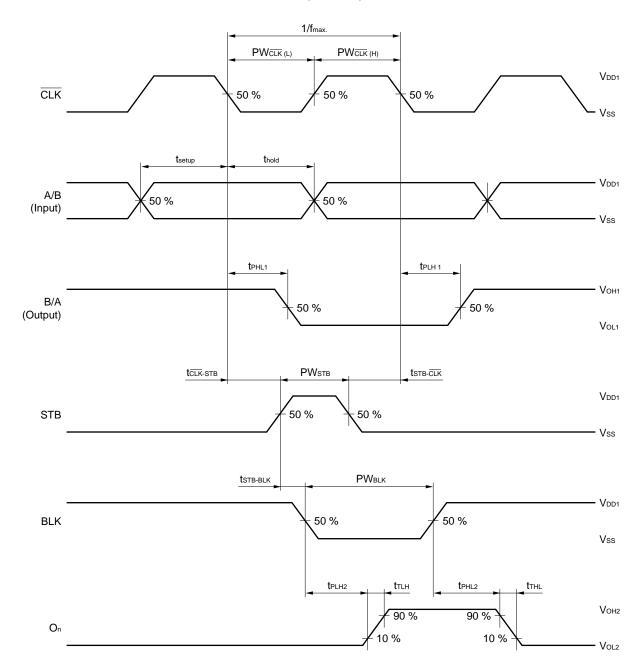

# SWITCHING CHARACTERISTICS (TA = 25 °C, $V_{DD1}$ = 5.0 V, $V_{DD2}$ = 125 V, $V_{SS}$ = 0 V, $I_{DD1}$ = 125 V, $I_{DD2}$ = 12

| Item                    | Symbol           | Condition                                                                   | MIN. | TYP. | MAX. | Unit |

|-------------------------|------------------|-----------------------------------------------------------------------------|------|------|------|------|

| Transmission delay time | tPHL1            | $\overline{CLK} \downarrow \to A/B$                                         |      |      | 110  | ns   |

|                         | <b>t</b> PLH1    |                                                                             |      |      | 110  | ns   |

|                         | tPHL2            | $\overline{\text{BLK}} \downarrow \rightarrow \text{O}_1 \text{ to O}_{32}$ |      |      | 300  | ns   |

|                         | tPLH2            |                                                                             |      |      | 300  | ns   |

| Fall time               | tтнL             | O <sub>1</sub> to O <sub>32</sub>                                           |      |      | 600  | ns   |

| Rise time               | tтьн             | O <sub>1</sub> to O <sub>32</sub>                                           |      |      | 500  | ns   |

| Maximum clock frequency | f <sub>max</sub> | With cascading, Duty = 50 %                                                 | 8.0  |      |      | MHz  |

| Input capacitance       | Сі               |                                                                             |      |      | 15   | pF   |

# TIMING REQUIREMENTS (TA = $-40 \text{ to } +85 ^{\circ}\text{C}$ , VDD1 = 4.5 to 5.5 V, Vss = 0 V, tr = tf = 10 ns)

| Item               | Symbol            | Condition                                              | MIN.  | TYP. | MAX. | Unit |

|--------------------|-------------------|--------------------------------------------------------|-------|------|------|------|

| Clock pulse width  | PWclk             |                                                        | 40    |      |      | ns   |

| Strobe pulse width | PWstB             |                                                        | 80    |      |      | ns   |

| Blank pulse width  | PW <sub>BLK</sub> |                                                        | 1 500 |      |      | ns   |

| Data setup time    | tsetup            |                                                        | 15    |      |      | ns   |

| Data hold time     | thold             |                                                        | 30    |      |      | ns   |

| Clock-strobe time  | tclк-sтв          | $\overline{CLK} \downarrow \to STB \uparrow$           | 45    |      |      | ns   |

| Strobe-clock time  | tstb-CLK          | $STB \downarrow \rightarrow \overline{CLK} \downarrow$ | 45    |      |      | ns   |

| Strobe-blank time  | tsтв-вцк          | STB $\uparrow \rightarrow$ BLK $\downarrow$            | 80    |      |      | ns   |

# SWITCHING CHARACTERISTIC WAVEFORM (R/L = H)

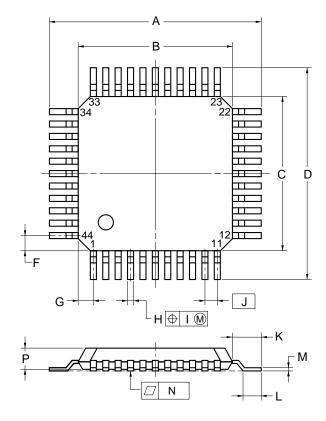

# **PACKAGE DRAWINGS**

# 44 PIN PLASTIC QFP (Unit: mm)

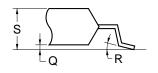

detail of lead end

#### NOTE

Each lead centerline is located within 0.15 mm (0.006 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| Α    | 13.6±0.4               | $0.535^{+0.017}_{-0.016}$ |

| В    | 10.0±0.2               | $0.394^{+0.008}_{-0.009}$ |

| С    | 10.0±0.2               | $0.394^{+0.008}_{-0.009}$ |

| D    | 13.6±0.4               | $0.535^{+0.017}_{-0.016}$ |

| F    | 1.0                    | 0.039                     |

| G    | 1.0                    | 0.039                     |

| Н    | 0.35±0.10              | 0.014+0.004               |

| - 1  | 0.15                   | 0.006                     |

| J    | 0.8 (T.P.)             | 0.031 (T.P)               |

| К    | 1.8±0.2                | $0.071^{+0.008}_{-0.009}$ |

| L    | 0.8±0.2                | 0.031+0.009               |

| М    | $0.15^{+0.10}_{-0.05}$ | $0.006^{+0.004}_{-0.003}$ |

| N    | 0.10                   | 0.004                     |

| Р    | 2.7                    | 0.106                     |

| Q    | 0.1±0.1                | 0.004±0.004               |

| R    | 5°±5°                  | 5°±5°                     |

| S    | 3.0 MAX.               | 0.119 MAX.                |

P44GB-80-3B4-3

#### RECOMMENDED SOLDERING CONDITIONS

This product should be soldered and mounted under the conditions recommended below.

For soldering methods and conditions other than those recommended, please contact your NEC sales representative.

#### SURFACE MOUNT TYPE

For details of recommended soldering conditions, refer to the information document "Semiconductor Device Mounting Technology Manual" (C10535E).

#### $\mu$ PD16326GB-3B4

| Soldering Method    | Soldering Conditions                                                                                                         | Recommended<br>Condition Symbol |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Infrared reflow     | Package peak temperature: 235 °C, Duration: 30 sec. MAX. (at 210 °C or above), Number of times: Twice, Time limit: None Note | IR35-00-2                       |

| VPS                 | Package peak temperature: 215 °C, Duration: 40 sec. MAX. (at 200 °C or above), Number of times: Twice, Time limit: None Note | VP15-00-2                       |

| Wave soldering      | Solder bath temperature: 260 °C MAX., Duration: 10 sec. MAX., Number of times: Once, Time limit: None Note                   | WS60-00-1                       |

| Pin partial heating | Pin partial temperature: 300 °C MAX., Duration: 10 sec. MAX., Time limit: None <sup>Note</sup>                               |                                 |

Note For the storage period after dry-pack decapsulation, storage conditions are max. 25 °C, 65 % RH.

Caution Use of more than one soldering method should be avoided (except in the case of pin partial heating).

#### **REFERENCES**

NEC Semiconductor Device Reliability/Quality Control System (IEI-1212) Quality Grade on NEC Semiconductor Devices (IEI-1209)

[MEMO]

[MEMO]

[MEMO]

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.